## EE 330 Lecture 42

## **Digital Circuits**

- Propagation Delay with Various Sizing

- Optimally driving large capacitive loads

- Logic Effort Method for Signal Propagation

## Spring 2024 Exam Schedule

Exam 1 Friday Feb 16

Exam 2 Friday March 8

Exam 3 Friday April 19

Final Exam Tuesday May 7 7:30 AM - 9:30

**AM**

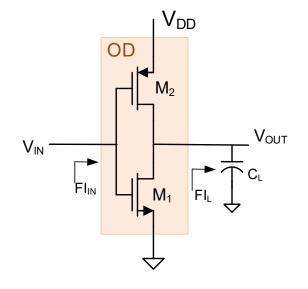

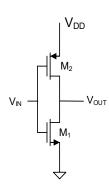

## Overdrive Factors

Scaling widths of ALL devices by constant (W<sub>scaled</sub>=WxOD) will change "drive" capability relative to that of the reference inverter but not change relative value of  $t_{\rm HL}$  and  $t_{\rm LH}$

$$R_{PD} = \frac{L_1}{\mu_n C_{OX} W_1 (V_{DD} - V_{Tn})} = \frac{R_{PD}}{OD}$$

$$R_{PDOD} = \frac{L_1}{\mu_n C_{OX} [OD \bullet W_1] (V_{DD} - V_{Tn})} = \frac{R_{PD}}{OD}$$

$$R_{PU} = \frac{L_2}{\mu_p C_{OX} W_2 \left(V_{DD} + V_{Tp}\right)}$$

$$R_{PUOD} = \frac{L_2}{\mu_p C_{OX} \left[OD \bullet W_2\right] \left(V_{DD} + V_{Tp}\right)} = \frac{R_{PU}}{OD}$$

$$R_{PUOD} = \frac{L_2}{\mu_p C_{OX} [OD \bullet W_2] (V_{DD} + V_{Tp})} = \frac{R_{PU}}{OD}$$

$$\mathbf{t}_{PROP} = \mathbf{t}_{REF} \bullet \mathbf{FI}_{L} \bullet \frac{1}{\mathbf{OD}}$$

Scaling widths of ALL devices by constant will change Fl<sub>IN</sub> to gate by OD

$${\sf C_{IN}} {=} {\sf C_{OX}} \big( {\sf W_1\!L_1\!+\!W_2\!L_2} \big)$$

$$C_{\text{INOD}} = C_{\text{OX}} ([O D \bullet W_1] L_1 + [O D \bullet W_2] L_2) = O D \bullet C_{\text{IN}}$$

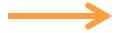

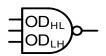

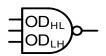

### **Asymmetric Overdrive**

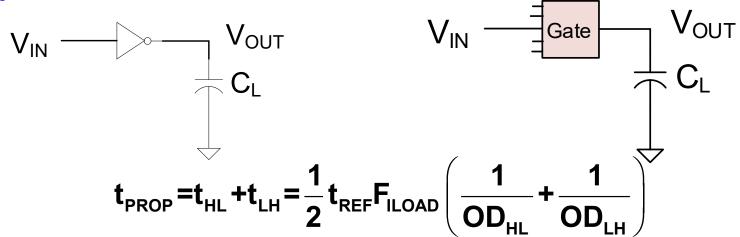

### When propagating through n stages:

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \left( \frac{1}{2} \sum_{\mathsf{k=1}}^{\mathsf{n}} \mathbf{F}_{\mathsf{l}(\mathsf{k+1})} \left( \frac{1}{\mathsf{OD}_{\mathsf{HLk}}} + \frac{1}{\mathsf{OD}_{\mathsf{LHk}}} \right) \right)$$

## Propagation Delay with Over-drive Capability

### **Example**

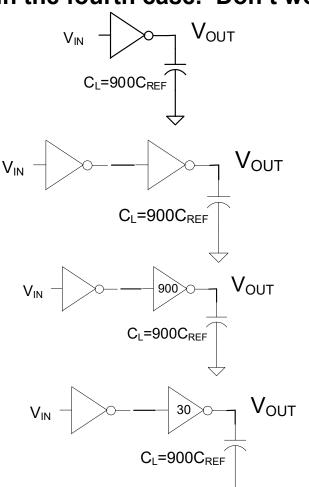

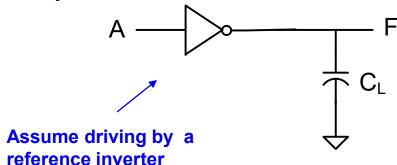

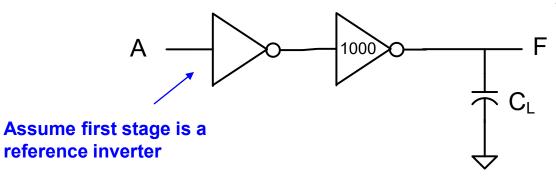

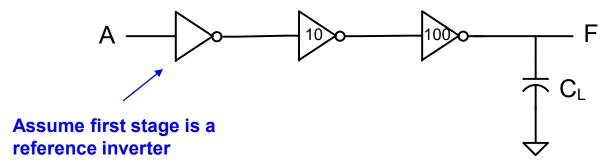

Compare the propagation delays. Assume the OD is 900 in the third case and 30 in the fourth case. Don't worry about the extra inversion at this time.

$$t_{PROP} = 900t_{REF}$$

$$t_{\mathsf{PROP}} \textbf{=} \ t_{\mathsf{REF}} + 900 t_{\mathsf{REF}} = 901 t_{\mathsf{REF}}$$

$$t_{\text{PROP}} \text{=} 900t_{\text{REF}} + t_{\text{REF}} = 901t_{\text{REF}}$$

$$t_{\text{PROP}} \hspace{-0.5em}=\hspace{-0.5em} 30t_{\text{REF}} + 30t_{\text{REF}} = 60t_{\text{REF}}$$

- Dramatic reduction in t<sub>PROP</sub> is possible (input is driving same in all 3 cases)

- Will later determine what optimal number of stages and sizing is

**Review from Last Time**

## Propagation Delay in Multiple-Levels of Logic with Stage Loading

Will consider an example with the five cases

- Equal rise/fall (no overdrive)

- Equal rise/fall with overdrive

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

Will develop the analysis methods as needed

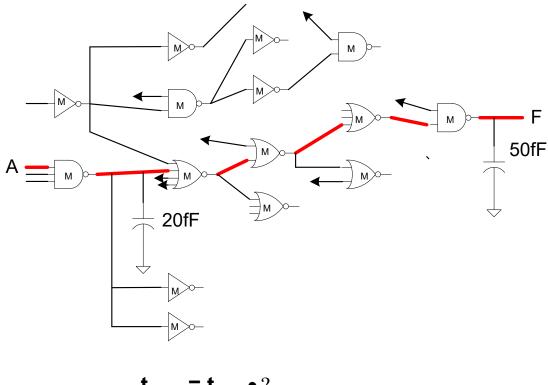

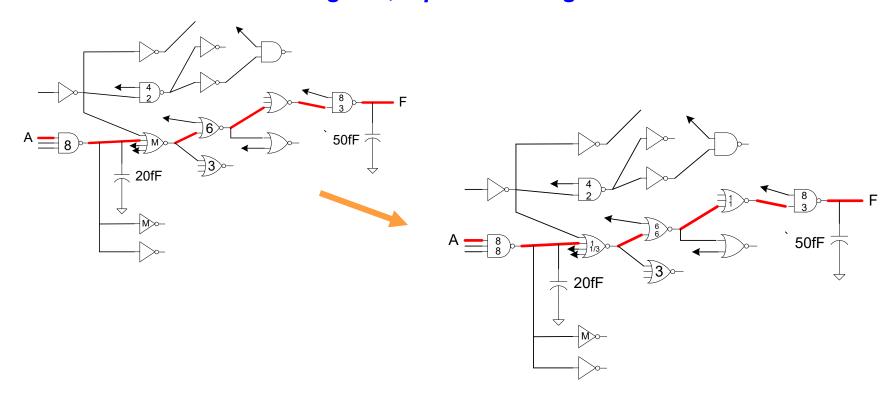

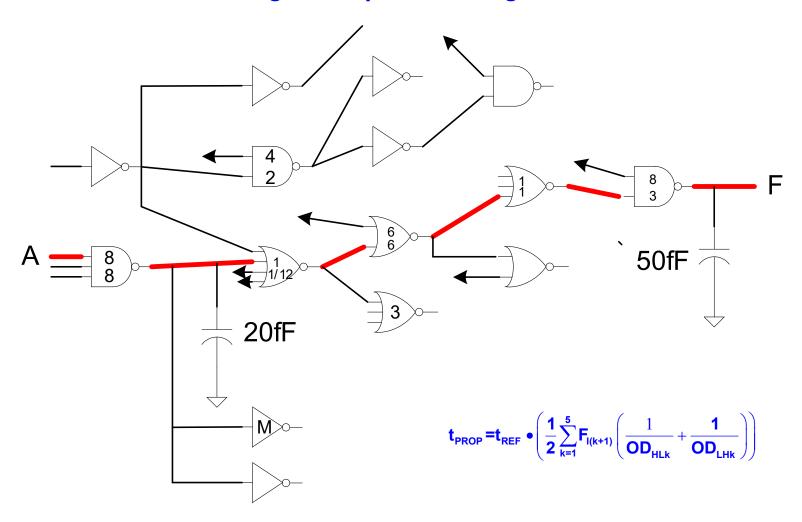

# Propagation Delay in Multiple-Levels of Logic with Stage Loading and Overdrives

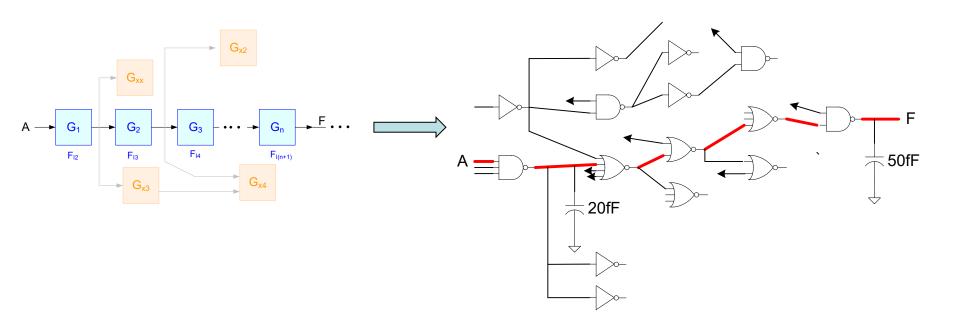

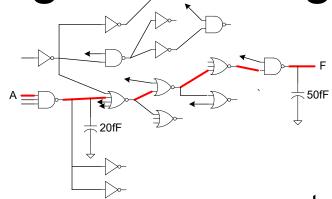

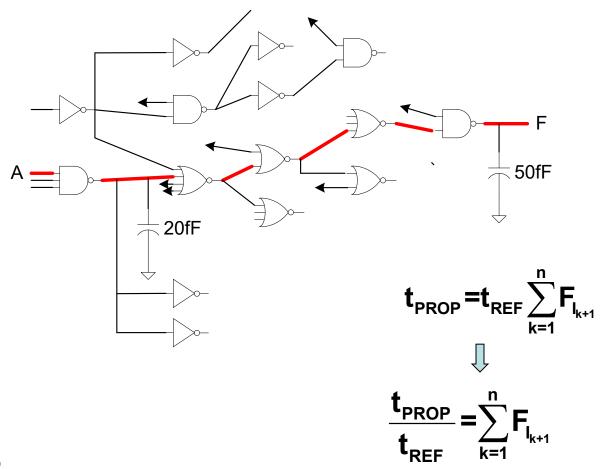

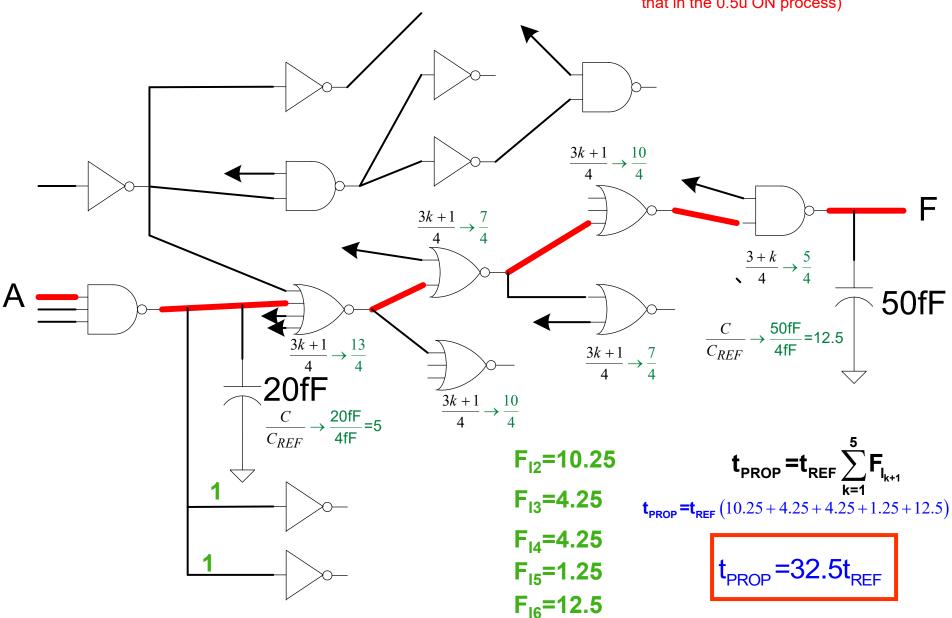

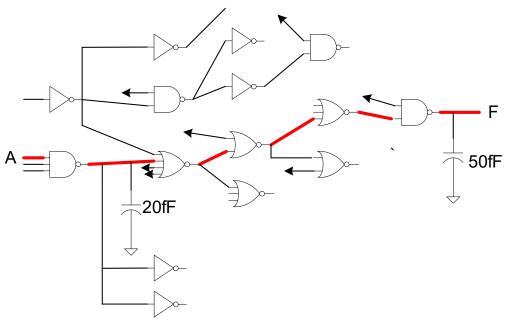

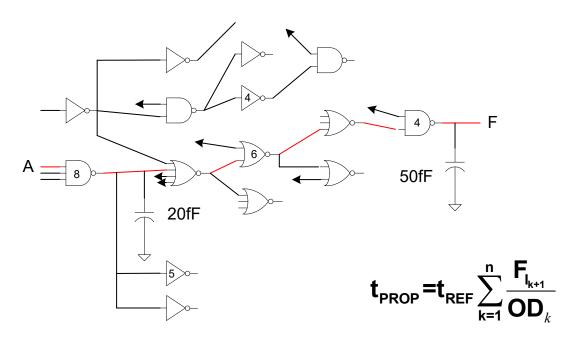

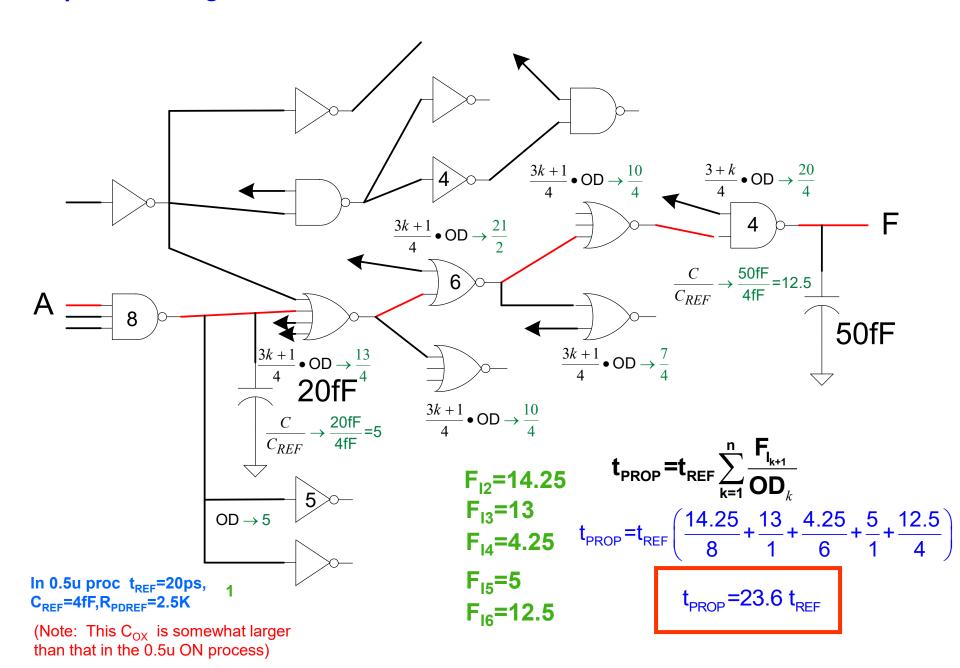

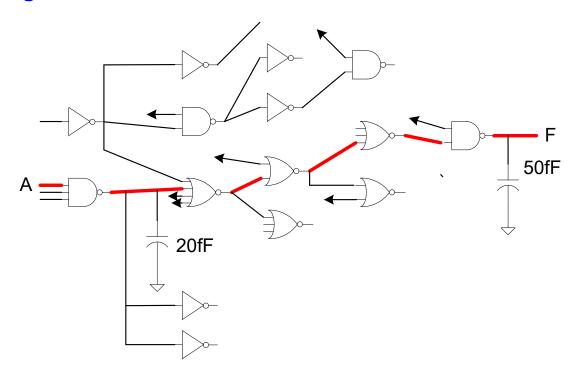

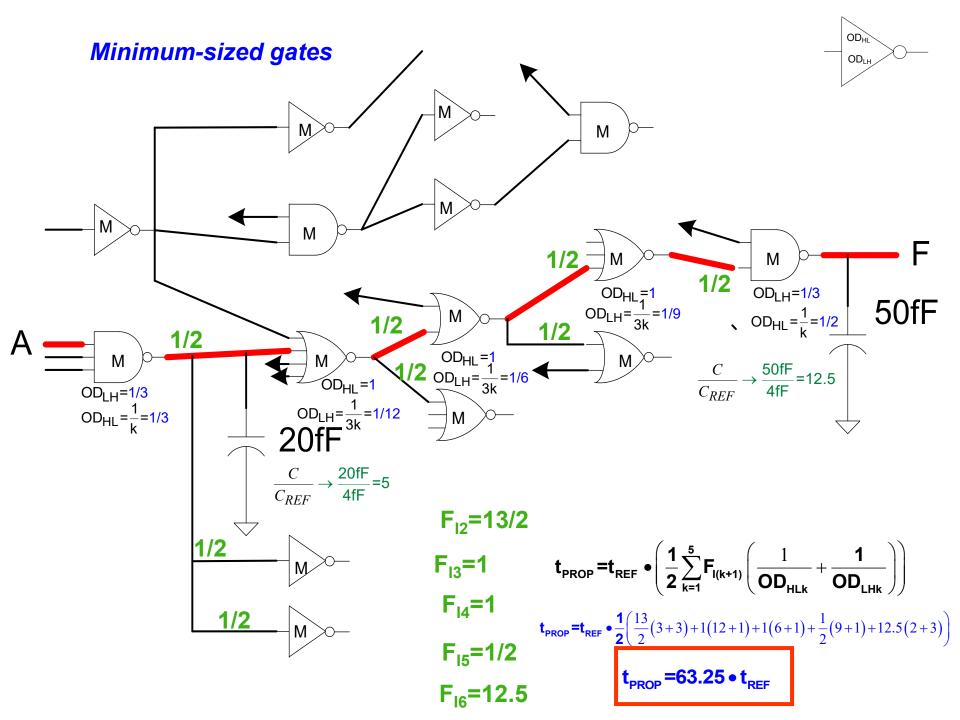

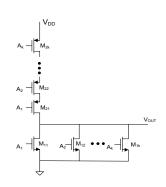

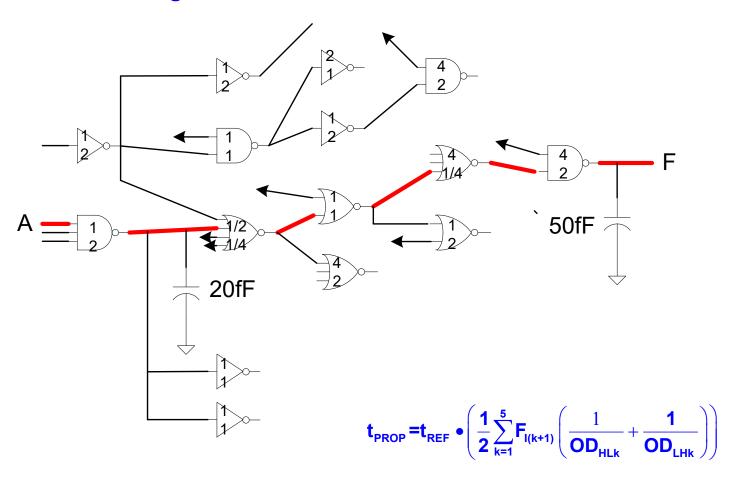

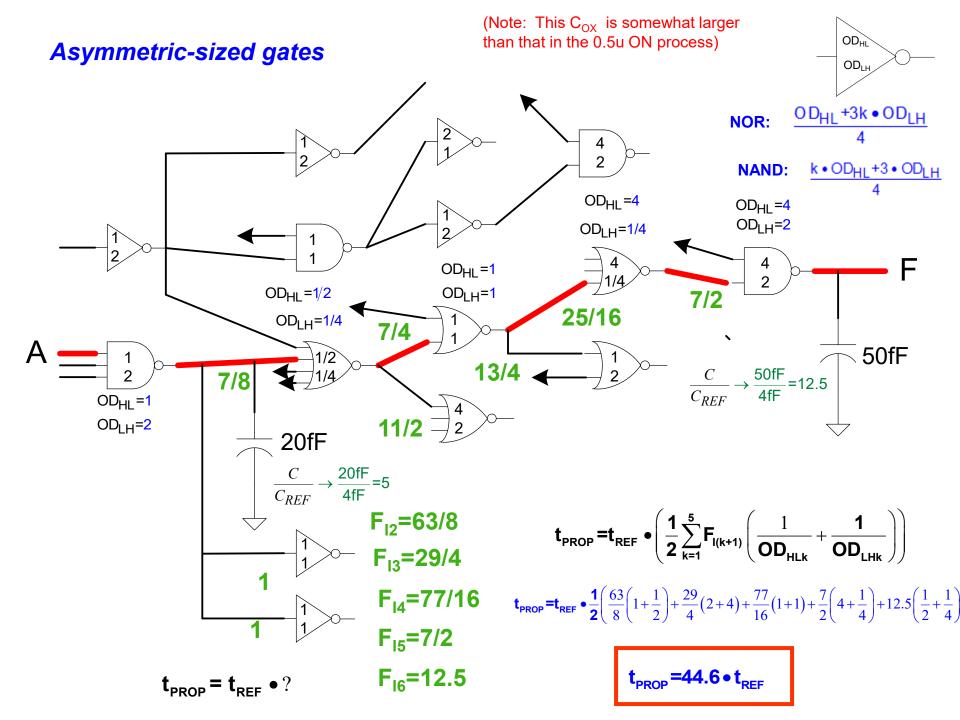

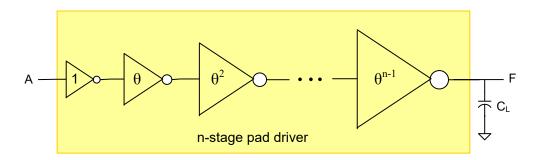

Will now consider A to F propagation for this circuit as an <u>example</u> with different overdrives

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} FI_{(k+1)}$$

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} \frac{F_{I(k+1)}}{OD}$$

$$t_{PROP} = ?$$

$$\mathbf{t}_{\text{PROP}} = \mathbf{t}_{\text{REF}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \mathbf{F}_{\text{I(k+1)}} \left( \frac{1}{\mathbf{OD}_{\text{HLk}}} + \frac{\mathbf{1}}{\mathbf{OD}_{\text{LHk}}} \right) \right)$$

$$t_{PROP} = ?$$

Equal rise-fall gates, no overdrive

### Equal rise-fall gates, no overdrive

|                                     | Equal Rise/Fall                    |  |

|-------------------------------------|------------------------------------|--|

| $C_{\text{IN}}/C_{\text{REF}}$      |                                    |  |

| Inverter                            | 1                                  |  |

| NOR                                 | 3k+1<br>4                          |  |

| NAND                                | 3+k<br>4                           |  |

| Overdrive                           |                                    |  |

| Inverter<br>HL                      | 1                                  |  |

| LH                                  | 1                                  |  |

| NOR<br>HL                           | 1                                  |  |

| LH                                  | 1                                  |  |

| NAND<br>HL                          | 1                                  |  |

| LH                                  | 1                                  |  |

| t <sub>PROP</sub> /t <sub>REF</sub> | $\sum_{k=1}^n \textbf{F}_{l(k+1)}$ |  |

### Equal rise-fall gates, no overdrive

In 0.5u proc  $t_{REF}$ =20ps,  $C_{REF}$ =4fF, $R_{PDREF}$ =2.5K

(Note: This  $C_{OX}$  is somewhat larger than that in the 0.5u ON process)

### Equal rise-fall gates, no overdrive

In 0.5u proc  $t_{REF}$ =20ps,  $C_{REF}$ =4fF, $R_{PDREF}$ =2.5K

(Note: This  $C_{OX}$  is somewhat larger than that in the 0.5u ON process)

$$t_{PROP} = 32.5t_{REF}$$

How does this propagation delay compare to that required for a propagation of a signal through 5-levels of logic with only reference inverters (load is a ref inverter instead of 50fF as well)?

$$A \longrightarrow t_{PROP} = 5t_{REF}$$

Loading can have a dramatic effect on propagation delay

• Equal rise/fall (no overdrive)

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} FI_{(k+1)}$$

$$\sum_{k=1}^{n} F_{k(k+1)}$$

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} \frac{F_{l(k+1)}}{OD_k}$$

$$t_{PROP} = ?$$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \left( \frac{1}{2} \sum_{\mathsf{k=1}}^{\mathsf{n}} \mathbf{F}_{\mathsf{I}(\mathsf{k+1})} \left( \frac{1}{\mathsf{OD}_{\mathsf{HLk}}} + \frac{1}{\mathsf{OD}_{\mathsf{LHk}}} \right) \right)$$

$$t_{PROP} = ?$$

Equal rise-fall gates, with overdrive

In 0.5u proc t<sub>REF</sub>=20ps, C<sub>REF</sub>=4fF,R<sub>PDREF</sub>=2.5K

(Note: This  $C_{\rm OX}$  is somewhat larger than that in the 0.5u ON process)

$$\frac{\mathbf{t}_{PROP}}{\mathbf{t}_{REF}} = \sum_{k=1}^{n} \frac{\mathbf{F}_{l_{k+1}}}{\mathbf{OD}_{k}}$$

### Equal rise-fall gates, with overdrive

|                                     | Equal Rise/Fall                             | Equal Rise/Fall (with OD)                                    |  |

|-------------------------------------|---------------------------------------------|--------------------------------------------------------------|--|

| $C_{\text{IN}}/C_{\text{REF}}$      |                                             |                                                              |  |

| Inverter                            | 1                                           | OD                                                           |  |

| NOR                                 | $\frac{3k+1}{4}$                            | 3k+1<br>4 • OD                                               |  |

| NAND                                | 3+k<br>4                                    | 3+k<br>4 • OD                                                |  |

| Overdrive                           |                                             |                                                              |  |

| Inverter<br>HL                      | 1                                           | OD                                                           |  |

| LH<br>NOR<br>HL                     | 1                                           | OD                                                           |  |

|                                     | 1                                           | OD                                                           |  |

| LH                                  | 1                                           | OD                                                           |  |

| NAND<br>HL                          | 1                                           | OD                                                           |  |

| LH                                  | 1                                           | OD                                                           |  |

| t <sub>PROP</sub> /t <sub>REF</sub> | $\sum_{k=1}^n \mathbf{F}_{\mathbf{I}(k+1)}$ | $\sum_{k=1}^{n} \frac{\textbf{F}_{l(k+1)}}{\textbf{OD}_{k}}$ |  |

#### Equal rise-fall gates, with overdrive

#### Minimum-sized gates

In 0.5u proc  $t_{REF}$ =20ps,  $C_{REF}$ =4fF, $R_{PDREF}$ =2.5K

$$t_{PROP} = t_{REF} \bullet ?$$

- Equal rise/fall (no overdrive)

- Equal rise/fall with overdrive

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} Fl_{(k+1)}$$

$$\mathbf{t}_{PROP} = \mathbf{t}_{REF} \sum_{k=1}^{n} \frac{\mathbf{F}_{I(k+1)}}{\mathbf{OD}_{k}}$$

$$t_{PROP} = ?$$

$$\boldsymbol{t}_{\text{PROP}} = \boldsymbol{t}_{\text{REF}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \boldsymbol{F}_{\text{I(k+1)}} \left( \frac{1}{\text{OD}_{\text{HLk}}} + \frac{1}{\text{OD}_{\text{LHk}}} \right) \right)$$

$$t_{PROP} = ?$$

Minimum-sized gates

$t_{PROP} = t_{REF} \bullet ?$

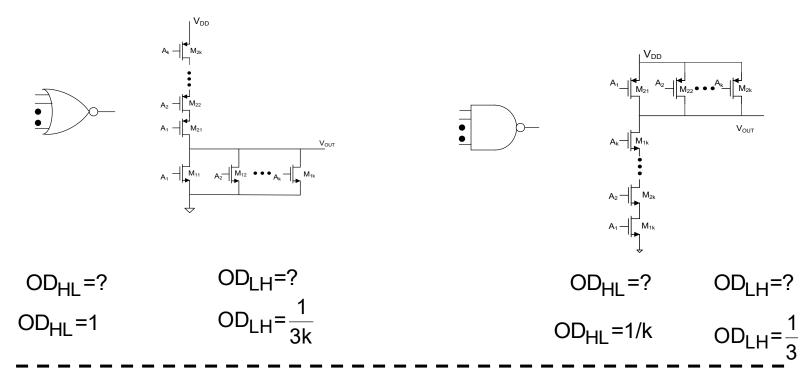

Observe that a minimum-sized gate is simply a gate with asymmetric overdrive

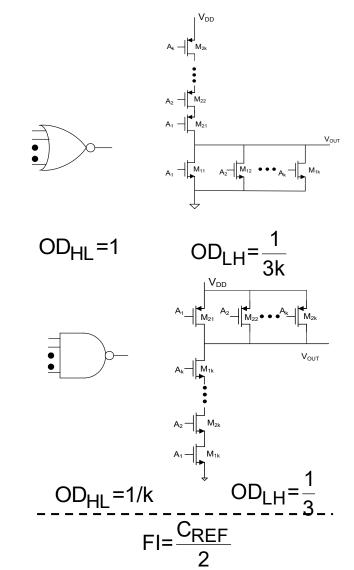

## Propagation Delay with Minimum-Sized Gates

Recall propagation delay for asymmetric overdrive:

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \left( \frac{1}{2} \sum_{\mathsf{k=1}}^{\mathsf{n}} \mathbf{F}_{\mathsf{I}(\mathsf{k+1})} \left( \frac{1}{\mathsf{OD}_{\mathsf{HLk}}} + \frac{1}{\mathsf{OD}_{\mathsf{LHk}}} \right) \right)$$

Thus for minimum-sized devices:

$$\frac{\mathbf{t}_{\mathsf{PROP}}}{\mathbf{t}_{\mathsf{REF}}} = \left(\frac{1}{2} \sum_{\mathsf{k=1}}^{\mathsf{n}} \mathbf{F}_{\mathsf{l}(\mathsf{k+1})} \left( \frac{1}{\mathsf{OD}_{\mathsf{HLk}}} + \frac{\mathbf{1}}{\mathsf{OD}_{\mathsf{LHk}}} \right) \right)$$

- Still need OD<sub>HL</sub> and OD<sub>LH</sub> for minimum-sized gates

- Still need FI for minimum-sized gates

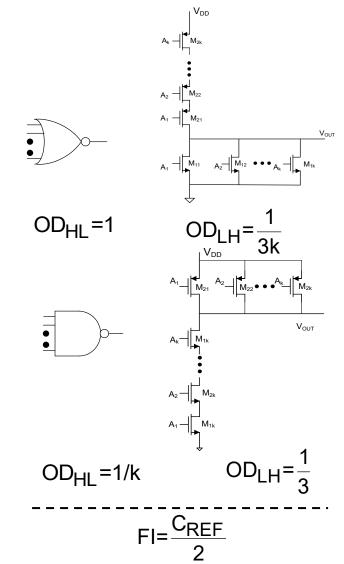

## Propagation Delay with minimum-sized gates

$FI=2C_{OX}W_{MIN}L_{MIN}$

$C_{REF} = 4C_{OX}W_{MIN}L_{MIN}$

$$FI = \frac{C_{REF}}{2}$$

### Minimum-sized gates

| C <sub>IN</sub> /C <sub>REF</sub>   | Equal Rise/Fall             | Equal Rise/Fall<br>(with OD)               | Minimum Sized |

|-------------------------------------|-----------------------------|--------------------------------------------|---------------|

|                                     | 4                           | OD                                         |               |

| Inverter                            | 1                           | OD                                         |               |

| NOR                                 | $\frac{3k+1}{4}$            | 3k+1<br>4 • OD                             |               |

| NAND                                | $\frac{3+k}{4}$             | 3+k<br>4 • OD                              |               |

| Overdrive                           |                             |                                            |               |

| Inverter                            |                             |                                            |               |

| HL                                  | 1                           | OD                                         |               |

| LH                                  | 1                           | OD                                         |               |

| NOR<br>HL                           | 1                           | OD                                         |               |

|                                     |                             |                                            |               |

| LH                                  | 1                           | OD                                         |               |

| NAND<br>HL                          | 1                           | OD                                         |               |

| LH                                  | 1                           | OD                                         |               |

| t <sub>PROP</sub> /t <sub>REF</sub> | $\sum_{k=1}^{n} F_{l(k+1)}$ | $\sum_{k=1}^{n} \frac{F_{l(k+1)}}{OD_{k}}$ |               |

### Minimum-sized gates

|                                | Equal Rise/Fall           | Equal Rise/Fall<br>(with OD)             | Minimum Sized                                                                                  |  |

|--------------------------------|---------------------------|------------------------------------------|------------------------------------------------------------------------------------------------|--|

| $C_{\text{IN}}/C_{\text{REF}}$ |                           |                                          |                                                                                                |  |

| Inverter                       | 1                         | OD                                       | 1/2                                                                                            |  |

| NOR                            | 3k+1<br>4                 | 3k+1<br>4 • OD                           | 1/2                                                                                            |  |

| NAND                           | $\frac{3+k}{4}$           | 3+k<br>4 • OD                            | 1/2                                                                                            |  |

| Overdrive                      |                           |                                          |                                                                                                |  |

| Inverter<br>HL                 | 1                         | OD                                       | 1                                                                                              |  |

| LH                             | 1                         | OD                                       | 1/3                                                                                            |  |

| NOR<br>HL                      | 1                         | OD                                       | 1                                                                                              |  |

| LH                             | 1                         | OD                                       | 1/(3k)                                                                                         |  |

| NAND<br>HL                     | 1                         | OD                                       | 1/k                                                                                            |  |

| LH                             | 1                         | OD                                       | 1/3                                                                                            |  |

| $t_{\sf PROP}/t_{\sf REF}$     | $\sum_{k=1}^n F_{l(k+1)}$ | $\sum_{k=1}^{n} \frac{F_{l(k+1)}}{OD_k}$ | $\frac{1}{2} \sum_{k=1}^{n} F_{I(k+1)} \left( \frac{1}{OD_{HLk}} + \frac{1}{OD_{LHk}} \right)$ |  |

### Minimum-sized gates

|                                     | Equal Rise/Fall                      | Equal Rise/Fall<br>(with OD)           | Minimum Sized                                                                                  |  |

|-------------------------------------|--------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------|--|

| $C_{\text{IN}}/C_{\text{REF}}$      |                                      |                                        |                                                                                                |  |

| Inverter                            | 1                                    | OD                                     | 1/2                                                                                            |  |

| NOR                                 | $\frac{3k+1}{4}$                     | 3k+1 • OD                              | 1/2                                                                                            |  |

| NAND                                | 3+k<br>4                             | 3+k<br>4 • OD                          | 1/2                                                                                            |  |

| Overdrive                           |                                      |                                        |                                                                                                |  |

| Inverter<br>HL                      | 1                                    | OD                                     | 1                                                                                              |  |

| LH                                  | 1                                    | OD                                     | 1/3                                                                                            |  |

| NOR<br>HL                           | 1                                    | OD                                     | 1                                                                                              |  |

| LH                                  | 1                                    | OD                                     | 1/(3k)                                                                                         |  |

| NAND<br>HL                          | 1                                    | OD                                     | 1/k                                                                                            |  |

| LH                                  | 1                                    | OD                                     | 1/3                                                                                            |  |

| t <sub>PROP</sub> /t <sub>REF</sub> | $\sum_{k=1}^{n} \mathbf{F}_{l(k+1)}$ | $\sum_{k=1}^n \frac{F_{l(k+1)}}{OD_k}$ | $\frac{1}{2} \sum_{k=1}^{n} F_{I(k+1)} \left( \frac{1}{OD_{HLk}} + \frac{1}{OD_{LHk}} \right)$ |  |

- Equal rise/fall (no overdrive)

- Equal rise/fall with overdrive

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} Fl_{(k+1)}$$

$$\mathbf{t}_{PROP} = \mathbf{t}_{REF} \sum_{k=1}^{n} \frac{\mathbf{F}_{I(k+1)}}{\mathbf{OD}_{k}}$$

$$\mathbf{t_{PROP}} = \mathbf{t_{REF}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \mathbf{F_{I(k+1)}} \left( \frac{1}{\mathbf{OD_{HLk}}} + \frac{\mathbf{1}}{\mathbf{OD_{LHk}}} \right) \right)$$

$$\mathbf{t_{PROP}} = \mathbf{t_{REF}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \mathbf{F_{I(k+1)}} \left( \frac{1}{\mathbf{OD_{HLk}}} + \frac{\mathbf{1}}{\mathbf{OD_{LHk}}} \right) \right)$$

$$t_{PROP} = ?$$

### Asymmetric-sized gates

### Asymmetric-sized gates

|                                                        | Equal Rise/Fall             | Equal Rise/Fall (with OD)                | Minimum Sized                                                                                    | Asymmetric OD<br>(OD <sub>HL</sub> , OD <sub>LH</sub> )                                        |

|--------------------------------------------------------|-----------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| $C_{\text{IN}}/C_{\text{REF}}$                         |                             |                                          |                                                                                                  |                                                                                                |

| Inverter                                               | 1                           | OD                                       | 1/2                                                                                              | ?                                                                                              |

| NOR                                                    | $\frac{3k+1}{4}$            | 3k+1                                     | 1/2                                                                                              | ?                                                                                              |

| NAND                                                   | $\frac{3+k}{4}$             | 3+k<br>4 • OD                            | 1/2                                                                                              | ?                                                                                              |

| Overdrive                                              |                             |                                          |                                                                                                  |                                                                                                |

| Inverter<br>HL                                         | 1                           | OD                                       | 1                                                                                                | $OD_HL$                                                                                        |

| LH                                                     | 1                           | OD                                       | 1/3                                                                                              | $OD_LH$                                                                                        |

| NOR<br>HL                                              | 1                           | OD                                       | 1                                                                                                | $OD_HL$                                                                                        |

| LH                                                     | 1                           | OD                                       | 1/(3k)                                                                                           | $OD_LH$                                                                                        |

| NAND<br>HL                                             | 1                           | OD                                       | 1/k                                                                                              | $OD_HL$                                                                                        |

| LH                                                     | 1                           | OD                                       | 1/3                                                                                              | $OD_LH$                                                                                        |

| t <sub>PROP</sub> /t <sub>REF</sub>                    | $\sum_{k=1}^{n} F_{l(k+1)}$ | $\sum_{k=1}^{n} \frac{F_{l(k+1)}}{OD_k}$ | $ \frac{1}{2} \sum_{k=1}^{n} F_{I(k+1)} \left( \frac{1}{OD_{HLk}} + \frac{1}{OD_{LHk}} \right) $ | $\frac{1}{2} \sum_{k=1}^{n} F_{l(k+1)} \left( \frac{1}{OD_{HLk}} + \frac{1}{OD_{LHk}} \right)$ |

| $t_{PROP}/t_{REF}                                    $ |                             |                                          |                                                                                                  |                                                                                                |

## Asymmetric-sized gates $C_{IN}/C_{REF}$

Inverter

**NOR**

**NAND**

### Asymmetric-sized gates $C_{IN}/C_{REF}$

$$\frac{C_{IN}}{C_{REF}} = \frac{C_{OX}W_{n}OD_{HL}L + C_{OX}(3W_{n})OD_{LH}L}{4C_{OX}W_{n}L} = \frac{OD_{HL} + 3OD_{LH}}{4}$$

#### **NOR**

$$\frac{C_{\text{IN}}}{C_{\text{REF}}} = \frac{C_{\text{OX}}W_{\text{n}}OD_{\text{HL}}L + C_{\text{OX}}(3kW_{\text{n}})OD_{\text{LH}}L}{4C_{\text{OX}}W_{\text{n}}L} = \frac{OD_{\text{HL}} + 3kOD_{\text{LH}}}{4}$$

#### **NAND**

$$\frac{C_{\text{IN}}}{C_{\text{REF}}} = \frac{C_{\text{OX}}kW_{\text{n}}OD_{\text{HL}}L + C_{\text{OX}}(3W_{\text{n}})OD_{\text{LH}}L}{4C_{\text{OX}}W_{\text{n}}L} = \frac{k \bullet OD_{\text{HL}} + 3OD_{\text{LH}}}{4}$$

### Asymmetric-sized gates

|                                                        | Equal Rise/Fall           | Equal Rise/Fall (with OD)                | Minimum Sized                                                                                    | Asymmetric OD<br>(OD <sub>HL</sub> , OD <sub>LH</sub> )                                        |

|--------------------------------------------------------|---------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|

| $C_{\text{IN}}/C_{\text{REF}}$                         |                           |                                          |                                                                                                  |                                                                                                |

| Inverter                                               | 1                         | OD                                       | 1/2                                                                                              | OD <sub>HL</sub> +3 • OD <sub>LH</sub> 4                                                       |

| NOR                                                    | $\frac{3k+1}{4}$          | 3k+1                                     | 1/2                                                                                              | ■ · · · · · · · · · · · · · · · · · · ·                                                        |

| NAND                                                   | $\frac{3+k}{4}$           | 3+k                                      | 1/2                                                                                              | $\frac{OD_{HL} + 3k \bullet OD_{LH}}{4} \\ \frac{k \bullet OD_{HL} + 3 \bullet OD_{LH}}{4}$    |

| Overdrive                                              |                           |                                          |                                                                                                  |                                                                                                |

| Inverter<br>HL                                         | 1                         | OD                                       | 1                                                                                                | $OD_HL$                                                                                        |

| LH                                                     | 1                         | OD                                       | 1/3                                                                                              | $OD_LH$                                                                                        |

| NOR<br>HL                                              | 1                         | OD                                       | 1                                                                                                | $OD_HL$                                                                                        |

| LH                                                     | 1                         | OD                                       | 1/(3k)                                                                                           | $OD_LH$                                                                                        |

| NAND<br>HL                                             | 1                         | OD                                       | 1/k                                                                                              | $OD_HL$                                                                                        |

| LH                                                     | 1                         | OD                                       | 1/3                                                                                              | $OD_LH$                                                                                        |

| $t_{PROP}/t_{REF}$                                     | $\sum_{k=1}^n F_{I(k+1)}$ | $\sum_{k=1}^{n} \frac{F_{l(k+1)}}{OD_k}$ | $ \frac{1}{2} \sum_{k=1}^{n} F_{I(k+1)} \left( \frac{1}{OD_{HLk}} + \frac{1}{OD_{LHk}} \right) $ | $\frac{1}{2} \sum_{k=1}^{n} F_{l(k+1)} \left( \frac{1}{OD_{HLk}} + \frac{1}{OD_{LHk}} \right)$ |

| $t_{PROP}/t_{REF}                                    $ |                           |                                          |                                                                                                  |                                                                                                |

#### Asymmetric-sized gates

- Equal rise/fall (no overdrive)

- Equal rise/fall with overdrive

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} Fl_{(k+1)}$$

$$\mathbf{t}_{PROP} = \mathbf{t}_{REF} \sum_{k=1}^{n} \frac{\mathbf{F}_{I(k+1)}}{\mathbf{OD}_{k}}$$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \mathbf{F}_{\mathsf{I}(\mathsf{k+1})} \left( \frac{1}{\mathsf{OD}_{\mathsf{HLk}}} + \frac{1}{\mathsf{OD}_{\mathsf{LHk}}} \right) \right)$$

$$\boldsymbol{t_{\text{PROP}}} = \boldsymbol{t_{\text{REF}}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \boldsymbol{F_{\text{I(k+1)}}} \left( \frac{1}{\boldsymbol{OD_{\text{HLk}}}} + \frac{\boldsymbol{1}}{\boldsymbol{OD_{\text{LHk}}}} \right) \right)$$

$$t_{PROP} = ?$$

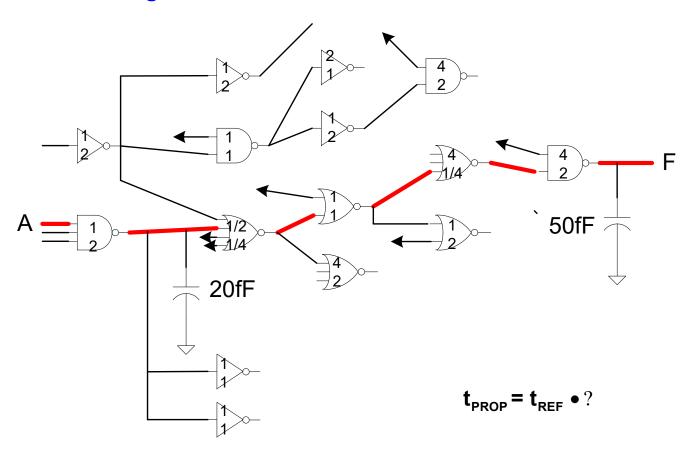

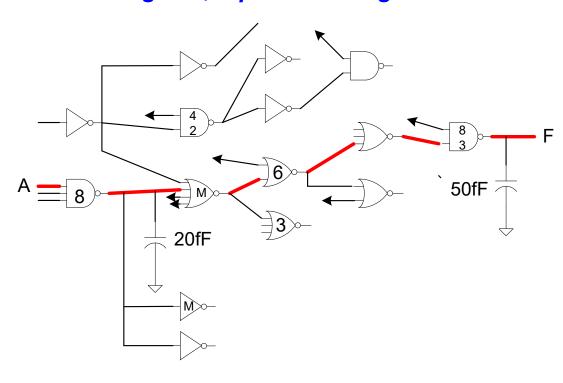

Mixture of Minimum-sized gates, equal rise/fall gates and OD

$$t_{PROP} = t_{REF} \bullet ?$$

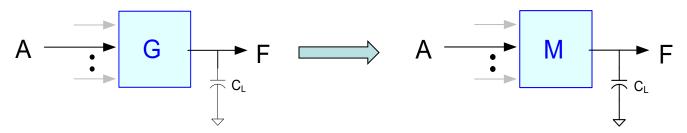

# **Driving Notation**

• Equal rise/fall (no overdrive)

• Equal rise/fall with overdrive

Minimum Sized

M — 1 1/3 —

Asymmetric Overdrive

Mixture of Minimum-sized gates, equal rise/fall gates and OD

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \left( \frac{1}{2} \sum_{k=1}^{5} \mathbf{F}_{\mathsf{I}(\mathsf{k+1})} \left( \frac{1}{\mathsf{OD}_{\mathsf{HLk}}} + \frac{1}{\mathsf{OD}_{\mathsf{LHk}}} \right) \right)$$

Mixture of Minimum-sized gates, equal rise/fall gates and OD

- Equal rise/fall (no overdrive)

- Equal rise/fall with overdrive

- Minimum Sized

- Asymmetric overdrive

- Combination of equal rise/fall, minimum size and overdrive

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} FI_{(k+1)}$$

$$\mathbf{t}_{PROP} = \mathbf{t}_{REF} \sum_{k=1}^{n} \frac{\mathbf{F}_{l(k+1)}}{\mathbf{OD}_{k}}$$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \mathbf{F}_{\mathsf{I}(\mathsf{k+1})} \left( \frac{1}{\mathsf{OD}_{\mathsf{HLk}}} + \frac{1}{\mathsf{OD}_{\mathsf{LHk}}} \right) \right)$$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \mathbf{F}_{\mathsf{I}(k+1)} \left( \frac{1}{\mathsf{OD}_{\mathsf{HLk}}} + \frac{1}{\mathsf{OD}_{\mathsf{LHk}}} \right) \right)$$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \mathbf{F}_{\mathsf{I}(k+1)} \left( \frac{1}{\mathsf{OD}_{\mathsf{HLk}}} + \frac{1}{\mathsf{OD}_{\mathsf{LHk}}} \right) \right)$$

|                    |                                      | 1/3                                        |                                                                                                   | OD <sub>HL</sub>                                                                                                          |

|--------------------|--------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

|                    | Equal Rise/Fall                      | Equal Rise/Fall<br>(with OD)               | Minimum Sized                                                                                     | Asymmetric OD<br>(OD <sub>HL</sub> , OD <sub>LH</sub> )                                                                   |

| $C_{IN}/C_{REF}$   |                                      |                                            |                                                                                                   |                                                                                                                           |

| Inverter           | 1                                    | OD                                         | 1/2                                                                                               | OD <sub>HL</sub> +3 • OD <sub>LH</sub>                                                                                    |

| NOR                | $\frac{3k+1}{4}$                     | 3k+1 • OD                                  | 1/2                                                                                               | 4<br>OD <sub>HL</sub> +3k • OD <sub>LH</sub>                                                                              |

| NAND               | 3+k<br>4                             | 3+k<br>4 • OD                              | 1/2                                                                                               | 4<br>k • OD <sub>HL</sub> +3 • OD <sub>LH</sub><br>4                                                                      |

| Overdrive          |                                      |                                            |                                                                                                   | 4                                                                                                                         |

| Inverter<br>HL     | 1                                    | OD                                         | 1                                                                                                 | $OD_HL$                                                                                                                   |

| LH                 | 1                                    | OD                                         | 1/3                                                                                               | $OD_LH$                                                                                                                   |

| NOR<br>HL          | 1                                    | OD                                         | 1                                                                                                 | $OD_HL$                                                                                                                   |

| LH                 | 1                                    | OD                                         | 1/(3k)                                                                                            | $OD_LH$                                                                                                                   |

| NAND<br>HL         | 1                                    | OD                                         | 1/k                                                                                               | $OD_HL$                                                                                                                   |

| LH                 | 1                                    | OD                                         | 1/3                                                                                               | $OD_LH$                                                                                                                   |

| $t_{PROP}/t_{REF}$ | $\sum_{k=1}^{n} \mathbf{F}_{l(k+1)}$ | $\sum_{k=1}^{n} \frac{F_{l(k+1)}}{OD_{k}}$ | $\boxed{\frac{1}{2}\sum_{k=1}^{n}F_{l(k+1)}\left(\frac{1}{OD_{HLk}} + \frac{1}{OD_{LHk}}\right)}$ | $\frac{1}{2} \sum_{k=1}^{n} \mathbf{F}_{I(k+1)} \left( \frac{1}{\mathbf{OD}_{HLk}} + \frac{1}{\mathbf{OD}_{LHk}} \right)$ |

# Digital Circuit Design

- Hierarchical Design

- Basic Logic Gates

- Properties of Logic Families

- Characterization of CMOS Inverter

- Static CMOS Logic Gates

- Ratio Logic

- Propagation Delay

- Simple analytical models

- FI/OD

- Logical Effort

- Elmore Delay

- Sizing of Gates

- The Reference Inverter

- Propagation Delay with Multiple Levels of Logic

- Optimal driving of Large Capacitive Loads

- Power Dissipation in Logic Circuits

- Other Logic Styles

- Array Logic

- Ring Oscillators

done partial

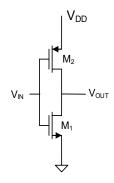

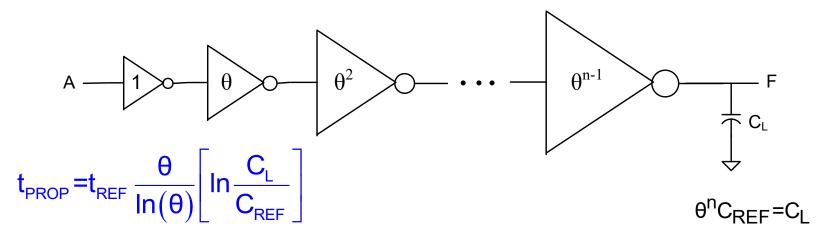

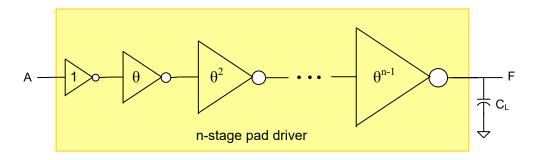

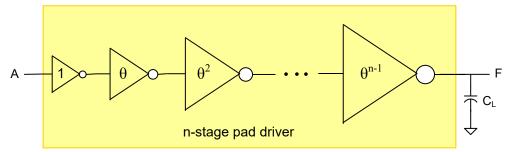

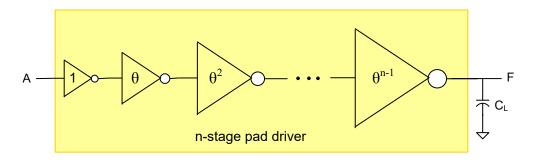

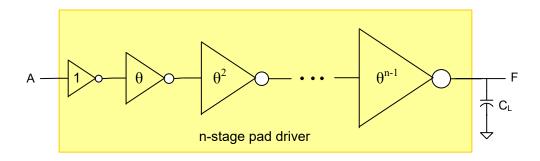

#### **Example**

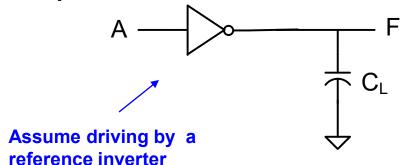

Assume  $C_L = 1000C_{REF}$

t<sub>PROP</sub>=?

#### **Example**

Assume C<sub>L</sub>=1000C<sub>REF</sub>

$t_{PROP} = 1000t_{REF}$

t<sub>PROP</sub> is too long!

#### **Example**

Assume C<sub>L</sub>=1000C<sub>REF</sub>

$$\mathbf{t_{PROP}} = ?$$

$$\mathbf{t_{PROP}} = \mathbf{t_{REF}} \sum_{k=1}^{2} \frac{\mathbf{F_{I(k+1)}}}{\mathbf{OD_k}}$$

$$\mathbf{t_{PROP}} = \mathbf{t_{REF}} \left( \frac{1}{1} 1000 + \frac{1}{1000} 1000 \right) = \mathbf{t_{REF}} \left( 1000 + 1 \right)$$

$$\mathbf{t_{PROP}} = \mathbf{t_{REF}} \left( 1001 \right)$$

Delay of second inverter is really small but overall delay is even longer than before!

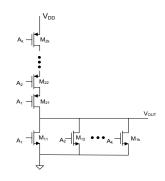

#### Example

Assume C<sub>L</sub>=1000C<sub>REF</sub>

$$\mathbf{t_{PROP}} = \mathbf{t_{REF}} \sum_{k=1}^{3} \frac{\mathbf{F_{I(k+1)}}}{\mathbf{OD_k}}$$

$$\mathbf{t_{PROP}} = \mathbf{t_{REF}} \left( \frac{1}{1} 10 + \frac{1}{10} 100 + \frac{1}{100} 1000 \right) = \mathbf{t_{REF}} \left( 10 + 10 + 10 \right)$$

$$\mathbf{t_{PROP}} = \mathbf{30t_{REF}}$$

Dramatic reduction is propagation delay (over a factor of 30!)

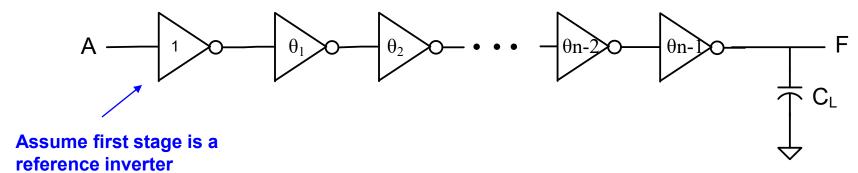

What is the fastest way to drive a large capacitive load?

Need to determine the number of stages, n, and the OD factors for each stage to minimize  $t_{PROP}$ .

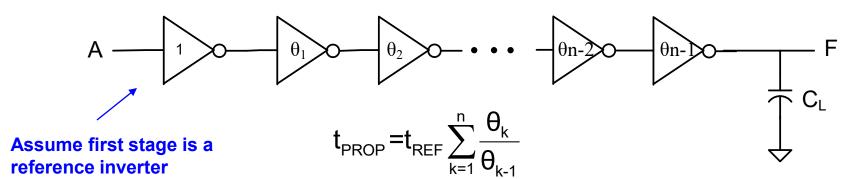

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} \frac{F_{I(k+1)}}{OD_{k}} \qquad t_{PROP} = t_{REF} \sum_{k=1}^{n} \frac{\theta_{k}}{\theta_{k-1}}$$

where

$$\theta_0=1$$

,  $\theta_n=C_L/C_{REF}$

This becomes an n-parameter optimization (minimization) problem!

Unknown parameters:  $\{\theta_1, \theta_2, ... \theta_{n-1}, n\}$

An n-parameter nonlinear optimization problem is generally difficult !!!!

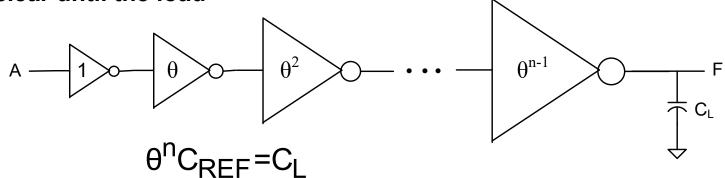

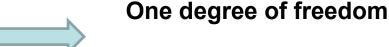

Order reduction strategy: Assume overdrive of stages increases by the same factor clear until the load

This becomes a 2-parameter optimization (minimization) problem! Unknown parameters:  $\{\theta, \Pi\}$

One constraint :  $\theta^{n}C_{REF} = C_{L}$

$$t_{PROP} = t_{REF} n\theta$$

$\theta^{n} C_{REF} = C_{L}$

$$\theta^{n}C_{REF} = C_{L}$$

$\longrightarrow$   $n = \frac{1}{\ln(\theta)}\ln\left(\frac{C_{L}}{C_{REF}}\right)$

Thus obtain an expression for  $t_{\text{PROP}}$  in terms of only  $\theta$

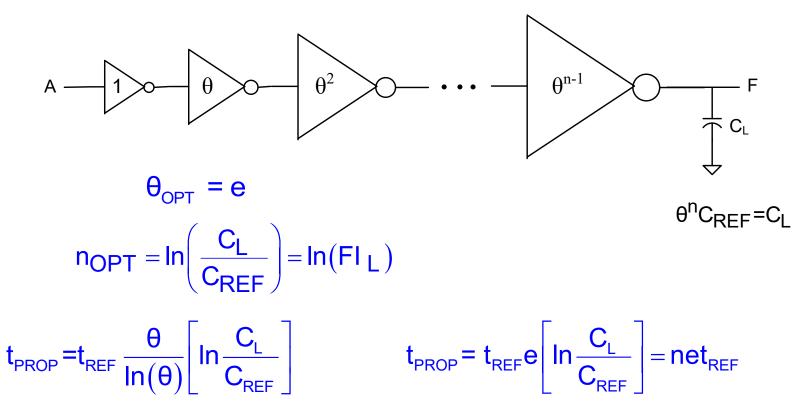

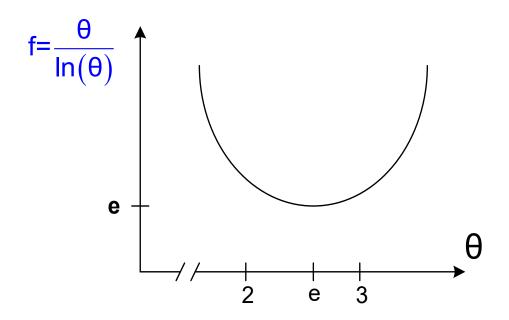

$$t_{PROP} = t_{REF} \frac{\theta}{\ln(\theta)} \left[ \ln \frac{C_L}{C_{REF}} \right]$$

It suffices to minimize the function

fices to minimize the function

$$f(\theta) = \frac{\theta}{\ln(\theta)}$$

$$\frac{df}{d\theta} = \frac{\ln(\theta) - \theta \cdot \left(\frac{1}{\theta}\right)}{\left(\ln(\theta)\right)^2} = 0$$

$$\ln(\theta) - 1 = 0 \rightarrow \theta = e$$

$$n = \frac{1}{\ln(\theta)} \ln \left( \frac{C_L}{C_{REF}} \right) \rightarrow n = \ln \left( \frac{C_L}{C_{REF}} \right) = \ln(FI_L)$$

- Since  $\theta_{\text{OPT}} = e$  is an irrational number, snap-size limitations in layout tools make it impossible to use the optimal scaling factor (even if n comes out to be an integer).

- Need a practical solution

A practical solution

- minimum at  $\theta$ =e but shallow inflection point for 2< $\theta$ <3

- practically pick  $\theta$ =2,  $\theta$ =2.5, or  $\theta$ =3

- since optimization may provide non-integer for n, must pick close integer

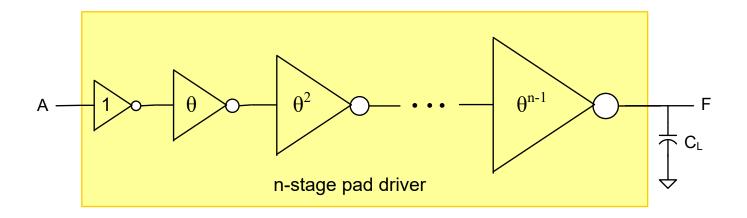

- Often termed a pad driver

- Often used to drive large internal busses as well

- Generally included in standard cells or in cell library

- Device sizes can become very large

- Odd number of stages will cause signal inversion but usually not a problem

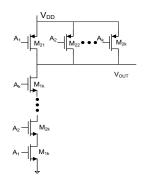

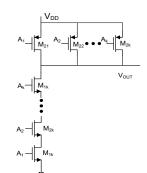

Example: Design a pad driver for driving a load capacitance of 10pF with equal rise/fall times, determine  $t_{PROP}$  for the pad driver, and compare this with the propagation delay for driving the pad with a minimum-sized reference inverter.

In 0.5u proc

$$t_{REF}$$

=20ps,  $C_{REF}$ =4fF, $R_{PDREF}$ =2.5K FI L=2500

$$n_{OPT} = ln \left(\frac{C_L}{C_{REF}}\right) = ln \left(\frac{10pF}{4fF}\right) = ln(2500) = 7.8$$

Select n=8,  $\theta$ =2.5

$$W_{nk} = 2.5^{k-1} \cdot W_{REF}, \quad W_{pk} = 3 \cdot 2.5^{k-1} \cdot W_{REF}$$

Example: Design a pad driver for driving a load capacitance of 10pF with equal rise/fall times, determine  $t_{PROP}$  for the pad driver, and compare this with the propagation delay for driving the pad with a minimum-sized reference inverter.

For

$$\theta = 2.5$$

, n=8  $W_{REF} = W_{MIN}$

$W_{nk} = 2.5^{k-1} \cdot W_{REF}$ ,  $W_{pk} = 3 \cdot 2.5^{k-1} \cdot W_{REF}$

$$L_n = L_p = L_{MIN}$$

| k | n-channel |       | p-channel |       |

|---|-----------|-------|-----------|-------|

| 1 | 1         | VVMIN | 3         | VVMIN |

| 2 | 2.5       | VVMIN | 7.5       | VVMIN |

| 3 | 6.25      | VVMIN | 18.75     | VVMIN |

| 4 | 15.6      | VVMIN | 46.9      | VVMIN |

| 5 | 39.1      | VVMIN | 117.2     | VVMIN |

| 6 | 97.7      | VVMIN | 293.0     | VVMIN |

| 7 | 244.1     | VVMIN | 732.4     | VVMIN |

| 8 | 610.4     | VVMIN | 1831.1    | VVMIN |

Note devices in last stage are very large!

Example: Design a pad driver for driving a load capacitance of 10pF with equal rise/fall times, determine  $t_{PROP}$  for the pad driver, and compare this with the propagation delay for driving the pad with a minimum-sized reference inverter.

$$\begin{array}{c} \text{In 0.5u proc } t_{\text{REF}}\text{=20ps,} \\ c_{\text{REF}}\text{=4fF,R}_{\text{PDREF}}\text{=2.5K} \end{array} \qquad W_{nk}\text{=}2.5^{k\text{-}1}\bullet\text{W}_{REF}, \qquad W_{pk}=3\bullet2.5^{k\text{-}1}\bullet\text{W}_{REF} \\ \\ t_{\text{PROP}}\cong n\theta t_{\text{REF}} \text{=}8\bullet2.5\bullet t_{\text{REF}}\text{=}20t_{\text{REF}} \end{array}$$

#### More accurately:

$$t_{PROP} = t_{REF} \left( \sum_{k=1}^{7} \theta + \frac{1}{\theta^7} \frac{C_L}{C_{REF}} \right) = t_{REF} \left( 17.5 + \frac{1}{610} 2500 \right) = 21.6 t_{REF}$$

#### More accurately:

$$t_{PROP} = t_{REF} \left( \sum_{k=1}^{7} \theta + \frac{1}{\theta^7} \frac{C_L}{C_{REF}} \right) = t_{REF} \left( 17.5 + \frac{1}{610} 2500 \right) = 21.6 t_{REF}$$

#### Possible modest improvement for determining n and $\theta$ after determining $n_{opt}$ :

Consider all possible combinations of  $\theta$  in { 2 , 2.5 , 3} and n in { INT(n<sub>opt</sub>), 1+INT(n<sub>opt</sub>)}

$$t_{\text{PROP}}\left(\theta,n\right) = t_{\text{REF}}\left(\sum_{k=1}^{n-1}\theta + \frac{1}{\theta^{n-1}}\frac{C_L}{C_{\text{REF}}}\right) = t_{\text{REF}}\left(\left(n-1\right)\theta + \frac{1}{\theta^{n-1}}FI_L\right)$$

Example: Design a pad driver for driving a load capacitance of 10pF with equal rise/fall times, determine  $t_{PROP}$  for the pad driver, and compare this with the propagation delay for driving the pad with a minimum-sized reference inverter.

If driven directly with the minimum-sized reference inverter

$$t_{PROP} = t_{REF} \frac{C_L}{C_{REF}} = 2500 t_{REF}$$

Note an improvement in speed by a factor of approximately

$$r = \frac{2500}{20} = 125$$

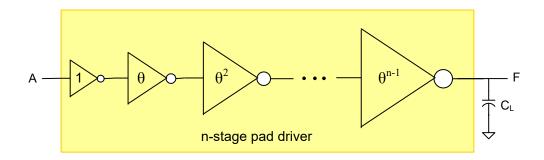

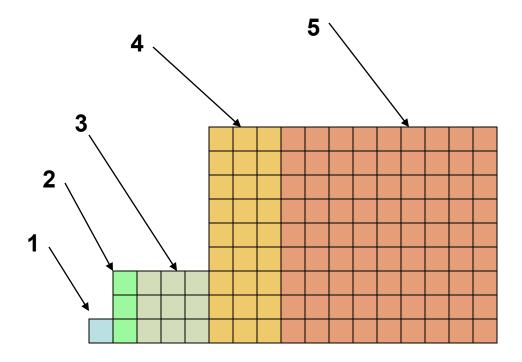

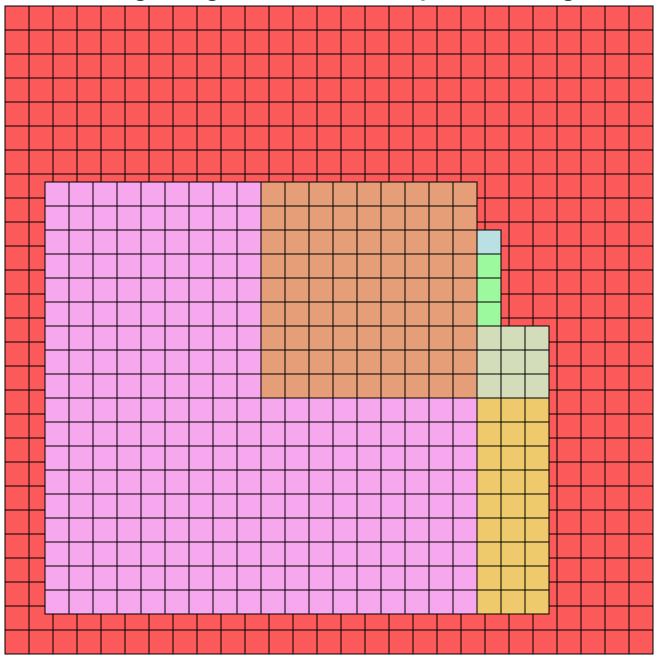

## Pad Driver Size Implications

Consider a 7-stage pad driver and assume  $\theta = 3$   $\Box$  : Area of Ref Inverter

#### Area of Last Stage Larger than that of all previous stages combined!

(Discussed in Chapter 4 of Text but definitions are not rigorous)

#### Logical effort

From Wikipedia, the free encyclopedia (Dec 8, 2021)

The method of **logical effort**, a term coined by Ivan Sutherland and Bob Sproull in 1991, is a straightforward technique used to estimate delay in a CMOS circuit. Used properly, it can aid in selection of gates for a given function (including the number of stages necessary) and sizing gates to achieve the minimum delay possible for a circuit.

(Discussed in Chapter 4 of Text but definitions are not rigorous)

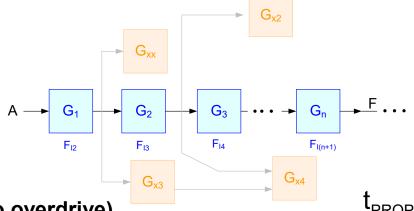

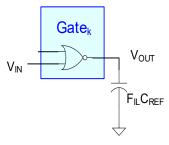

Propagation delay for equal rise/fall gates was derived to be

$$\mathbf{t}_{PROP} = \mathbf{t}_{REF} \sum_{k=1}^{n} \frac{\mathbf{F}_{l(k+1)}}{\mathbf{OD}_{k}}$$

Delay calculations with "logical effort" approach

Logical effort delay approach:

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \sum_{\mathsf{k}=1}^{n} \mathbf{f}_{\mathsf{k}}$$

$t_{PROP} = t_{REF} \sum_{k=1}^{n} f_k$  ( $t_{REF}$  scaling factor not explicitly stated in W\_H textbook. As defined in W\_H,  $f_k$  is dimensionless)

where  $f_k$  is the "effort delay" of stage k

$$f_k = g_k h_k$$

g<sub>k</sub>=logical effort

h<sub>k</sub>=electrical effort

$$\mathbf{t}_{PROP} = \mathbf{t}_{REF} \sum_{k=1}^{n} \mathbf{f}_{k} \qquad \mathbf{f}_{k} = \mathbf{g}_{k} \mathbf{h}_{k}$$

f<sub>k</sub> = "effort delay" of stage k

g<sub>k</sub>=logical effort

h<sub>k</sub>=electrical effort

Logic Effort is the ratio of the input capacitance of a gate to the input capacitance of an inverter that can deliver the same output current

Electrical Effort is the ratio of the gate load capacitance to the input capacitance of a gate

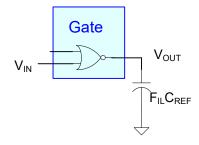

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} f_k \qquad f_k = g_k h_k$$

Logic Effort (g) is the ratio of the input capacitance of a gate to the input capacitance of an inverter that can deliver the same output current

Electrical Effort (h) is the ratio of the gate load capacitance to the input capacitance of a gate

$$g_k = \frac{C_{IN_k}}{C_{REF} \cdot OD_k}$$

$$g_k = \frac{C_{IN_k}}{C_{REF} \cdot OD_k} \qquad h_k = \frac{C_{REF} \cdot FI_{k+1}}{C_{IN_k}}$$

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} f_k \qquad f_k = g_k h_k$$

$$g_k = \frac{C_{IN_k}}{C_{REF} \cdot OD_k}$$

$$g_k = \frac{c_{IN_k}}{c_{REF} \cdot od_k} \qquad \qquad h_k = \frac{c_{REF} \cdot F_{I(k+1)}}{c_{IN_k}}$$

$$f_k = \left(\frac{c_{IN_k}}{c_{REF} \cdot c_{IN_k}}\right) \left(\frac{c_{REF} \cdot F_{I(k+1)}}{c_{IN_k}}\right)$$

$$f_k = \frac{F_1(k+1)}{OD_k}$$

$$t_{\mathsf{PROP}} = t_{\mathsf{REF}} \sum_{\mathsf{k}=1}^{\mathsf{n}} f_{\mathsf{k}} = t_{\mathsf{REF}} \sum_{\mathsf{k}=1}^{\mathsf{n}} g_{\mathsf{k}} h_{\mathsf{k}} = t_{\mathsf{REF}} \sum_{\mathsf{k}=1}^{\mathsf{n}} \frac{F_{\mathsf{l}(\mathsf{k}+1)}}{\mathsf{OD}_{\mathsf{k}}}$$

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} f_k = t_{REF} \sum_{k=1}^{n} g_k h_k = t_{REF} \sum_{k=1}^{n} \frac{F_{I(k+1)}}{OD_k}$$

- Note this expression is identical to what we have derived previously (t<sub>REF</sub> scaling factor not included in W\_H text)

- Probably more tedious to use the "Logical Effort" approach

- Extensions to asymmetric overdrive factors may not be trivial

- Extensions to include parasitics may be tedious as well

- Logical Effort is widely used throughout the industry

# Stay Safe and Stay Healthy!

### **End of Lecture 42**